Integrated circuit testing is a crucial step in ensuring chip quality, with the two main types of testing being CP testing (Chip Probing) and FT testing (Final Test). These testing methods span the front and back stages of chip production, evaluating both the wafer and the packaged final product.

The distinction between CP and FT testing can be likened to the production and packaging of agricultural products. CP testing is similar to a preliminary check of each fruit during harvest, removing those that are obviously bad, while FT testing occurs after packaging, serving as the final quality check to ensure the fruits can be safely delivered to market.

1. CP Testing (Chip Probing) — Preliminary Screening

CP testing refers to the electrical and functional testing of each chip unit (die) directly on the wafer before it is cut and packaged. This is a “probing” test aimed at early identification and removal of defective chips to avoid unnecessary subsequent costs.

1.1 Purpose of CP Testing

In the early stages of wafer manufacturing, the produced chips are not yet packaged, which is a time-consuming and expensive process. If all chips are packaged without preliminary screening, many defective chips will enter the packaging stage, increasing costs related to packaging and subsequent testing. Therefore, the main purposes of CP testing are:

- Identify and Remove Bad Dies: Through electrical performance and basic functional tests, defective chip units are eliminated early.

- Reduce Subsequent Process Costs: Avoid wasting packaging costs, as defective chips cannot be recovered once packaged.

- Monitor Front-End Process Yield: Testing results can evaluate the stability and quality of the wafer manufacturing process, providing data support for subsequent improvements.

1.2 Process of CP Testing

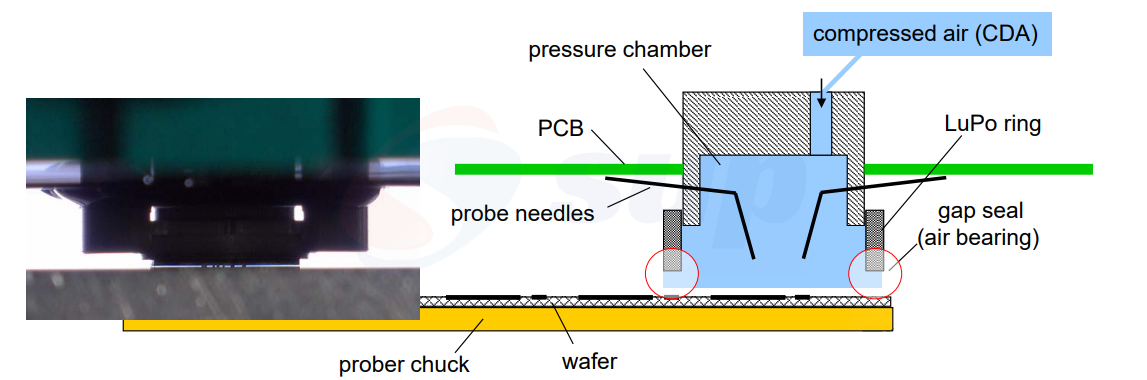

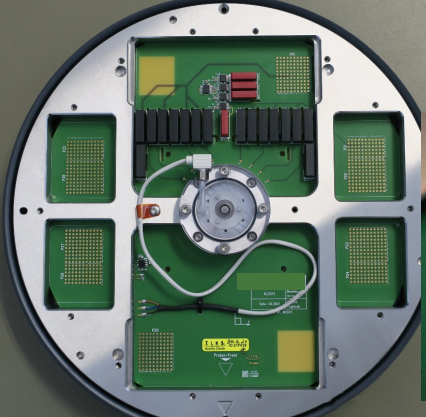

CP testing uses a probe card to transmit electrical signals to each chip unit, measuring their electrical performance through testing equipment. Typical test items include threshold voltage (Vt), on-resistance (Rdson), and leakage current (Idss).

1.3 Characteristics of CP Testing

- Test Objects: Each die on the wafer.

- Testing Phase: Conducted before the wafer is cut and packaged, part of the front-end process testing.

- Test Items: Focuses on basic electrical performance tests, with lower testing power; probe cards limit high current testing.

- Testing Challenges: Ensuring the precision of the probe card, dealing with probe interference, and challenges of parallel testing. Particularly in large-scale integrated circuits, ensuring the contact accuracy and stability of the probe card is a significant challenge.

2. FT Testing (Final Test) — Finished Product Inspection

FT testing involves testing the packaged chips to conduct comprehensive and rigorous functional and performance evaluations, ensuring that the chips meet design requirements and operate reliably in real-world applications.

2.1 Purpose of FT Testing

Packaged chips are the final product and must have all functions operating normally before leaving the factory. FT testing not only verifies the chip's functions but also tests its performance under extreme conditions. The goals of FT testing are:

- Ensure Packaging Quality: Check whether the packaging process has affected the chip, such as if pin connections are intact and whether electrical performance has changed.

- Comprehensive Function Verification: Ensure that all functions of the chip meet design specifications and customer requirements.

- Reliability Testing: Evaluate the chip's reliability under different temperature and pressure conditions, ensuring performance in actual application environments.

2.2 Process of FT Testing

FT testing is usually conducted using Automatic Test Equipment (ATE). The chips are placed on the testing platform via handlers and test sockets, performing tests that include electrical functions, performance metrics, and extreme condition evaluations. FT testing often includes temperature and pressure tests, simulating the chip's operation in high temperatures (e.g., 75°C or 90°C) or low temperatures (e.g., -20°C or -40°C).

2.3 Characteristics of FT Testing

- Test Objects: Finished chips that have been packaged.

- Testing Phase: Conducted as the final step after chip packaging.

- Test Items: More comprehensive functional tests with strict testing conditions. Common tests include functionality tests, electrical performance tests, power tests, and thermal stability tests.

- Testing Challenges: Ensuring the chip performs well in real-world conditions, especially under extreme temperatures. FT testing also checks power consumption and output performance, which cannot be fully tested during the CP phase.

3. Differences and Connections Between CP and FT Testing

3.1 Different Test Objects

CP testing primarily targets chip units on the wafer, i.e., unencapsulated bare chips. FT testing, on the other hand, focuses on the completed packaged chips.

3.2 Different Testing Stages

CP testing is conducted in the front-end process of wafer manufacturing, typically completed before wafer cutting. FT testing occurs in the final stage after chip packaging, ensuring the chips are ready for market.

3.3 Different Testing Purposes

The purpose of CP testing is to eliminate obviously defective chips, reduce subsequent packaging costs, and monitor wafer manufacturing yield. FT testing aims to ensure the functionality and reliability of chips in real-world applications, serving as the last checkpoint before shipping.

3.4 Different Test Items

CP testing mainly focuses on basic electrical performance tests, such as threshold voltage, on-resistance, and leakage current, which are relatively basic and involve lower power. FT testing covers a broader range of items, including functional tests, performance tests, and reliability tests, with higher power capabilities and more stringent environmental conditions.

3.5 Different Testing Conditions

CP testing is usually conducted at room temperature under relatively simple conditions. In contrast, FT testing requires evaluations under varying temperature conditions, particularly testing the stability and reliability of chips in high or low temperature environments.

4. Connections Between CP and FT Testing

Despite their different stages, CP and FT testing are two critical components of a complete testing process. Both share the common goal of ensuring the final quality and reliability of chips. For certain test items, CP testing can reduce the workload of FT testing. For example, basic electrical performance tests completed during CP can be excluded from FT, saving testing time and costs. Additionally, in some cases, CP testing can include repairs, such as laser repair technology to fix salvageable chips, further improving yield and reliability. FT testing does not have this repair capability; it is purely a detection phase, with any defective chips being discarded.

5. Future Trends of CP and FT Testing

With advancements in chip manufacturing and packaging technologies, more companies are attempting to reduce or even skip the CP testing phase, opting to perform only FT testing. While this approach saves on CP testing costs, it increases risks in subsequent packaging and testing stages, potentially leading to more defective finished chips. In the manufacturing of high-density memory devices, the role of CP testing is particularly critical. Through redundancy analysis in CP testing, it is possible to determine which parts of the chip need repair and enhance yield through laser repair, a process that cannot be achieved during FT.

6. Summary

CP testing and FT testing are indispensable parts of the integrated circuit testing process. CP testing eliminates defective chips during the wafer stage to reduce subsequent costs, while FT testing ensures that the functionality and performance of chips meet design requirements after packaging. Although there are differences in test objects, stages, and items, together they form the core process of chip quality control (PS: In the semiconductor field, testing involves a variety of processes. As a professional semiconductor equipment supplier, Supsemi offers a wide range of related Semiconductor Testing Equipment. We welcome you to reach out to us for more information and inquiries about purchasing.)

Contact: Bruce Liu

WhatsApp: +86-18059149998

Tel: +86-18059149998

Email: sales@supsemi.com

Add: Room 1402, Building 1, No. 89 Xibeilu, Xishancun, Xibei Street, Xinluo District, Longyan City, Fujian Province

We chat